### SANDIA REPORT

SAND2017-9980 Unlimited Release Printed September 2017

# ASC ATDM Level 2 Milestone #6015: Asynchronous Many-Task Software Stack Demonstration

Janine C. Bennett, Matthew T. Bettencourt, Robert L. Clay, Harold C. Edwards, Micheal W. Glass, David S. Hollman, Hemanth Kolla, Jonathan J. Lifflander, David J. Littlewood, Aram H. Markosyan, Stan G. Moore, Stephen L. Olivier, J. Antonio Perez, Eric T. Phipps, Francesco Rizzi, Nicole L. Slattengren, Daniel Sunderland, Jeremiah J. Wilke

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC., a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

Approved for public release; further dissemination unlimited.

Sandia National Laboratories

Level S

Issued by Sandia National Laboratories, operated for the United States Department of Energy by National Technology and Engineering Solutions of Sandia, LLC.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

| Telephone:       | (865) 576-8401             |

|------------------|----------------------------|

| Facsimile:       | (865) 576-5728             |

| E-Mail:          | reports@adonis.osti.gov    |

| Online ordering: | http://www.osti.gov/bridge |

Available to the public from U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd Springfield, VA 22161

Telephone:(800) 553-6847Facsimile:(703) 605-6900E-Mail:orders@ntis.fedworld.govOnline ordering:http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online

#### SAND2017-9980 Unlimited Release Printed September 2017

### ASC ATDM Level 2 Milestone #6015: Asynchronous Many-Task Software Stack Demonstration

Janine C. Bennett, Matthew T. Bettencourt, Robert L. Clay, Harold C. Edwards, Micheal W. Glass, David S. Hollman,

Hemanth Kolla, Jonathan J. Lifflander, David J. Littlewood, Aram H. Markosyan, Stan G. Moore, Stephen L. Olivier, J. Antonio Perez, Eric T. Phipps, Francesco Rizzi,

Nicole L. Slattengren, Daniel Sunderland, Jeremiah J. Wilke

#### Abstract

This report is an outcome of the ASC ATDM Level 2 Milestone 6015: Asynchronous Many-Task Software Stack Demonstration. It comprises a summary and in depth analysis of DARMA and a DARMA-compliant Asynchronous Many-Task (AMT) runtime software stack. Herein performance and productivity of the overall approach are assessed on benchmarks and proxy applications representative of the Sandia ATDM applications. As part of the effort to assess the perceived strengths and weaknesses of AMT models compared to more traditional methods, experiments were performed on ATS-1 (Advanced Technology Systems) test bed machines and Trinity. In addition to productivity and performance assessments, this report includes findings on the generality of DARMA's backend API as well as findings on interoperability with nodelevel and network-level system libraries. Together, this information provides a clear understanding of the strengths and limitations of the DARMA approach in the context of Sandia's ATDM codes, to guide our future research and development in this area.

## Acknowledgment

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC., a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA-0003525. Funding was provided as part of the Advanced Technology Detection and Mitigation (ATDM) program funded as part of the Advanced Simulation and Computing (ASC) program of the National Nuclear Security Administration (NNSA). Additional contributions come from the Exascale Computing Program (ECP) jointly funded by the U.S. Department of Energy (DOE) Office and Science and NNSA.

Access to Trinity and Mutrino systems was obtained through the Advanced Computing at Extreme Scale (ACES) program under allocation 137908. Special thanks goes to Ann Gentile, Jason Repnik, Nathan Gauntt, Jim Brandt, Joel Stevenson, David Kratzer, and Peter Lambhorn for technical support throughout the project. Additional runs were performed at the National Energy Research Scientific Computing Center (NERSC).

Special thanks goes to those who have provided insight through technical discussions throughout the full development of project including Phil Miller, Sanjay Kale, Sean Treichler, Timothy Mattson, David Richards, and Jeff Keasler.

# Contents

| Ex | ecuti | ve Sum   | mary                                                        | 23 |

|----|-------|----------|-------------------------------------------------------------|----|

| 1  | Intro | oductio  | n                                                           | 25 |

|    | 1.1   | Progra   | mmatic History                                              | 25 |

|    | 1.2   | Exasca   | le Drivers                                                  | 26 |

|    | 1.3   | FY15     | ATDM Level 2 Milestone                                      | 27 |

|    | 1.4   | FY17 1   | Milestone Outline                                           | 28 |

| 2  | DAI   | RMA O    | verview                                                     | 33 |

|    | 2.1   | Design   | Considerations                                              | 33 |

|    |       | 2.1.1    | Categories of Application Task Graphs                       | 34 |

|    | 2.2   | DARN     | A Execution Model                                           | 35 |

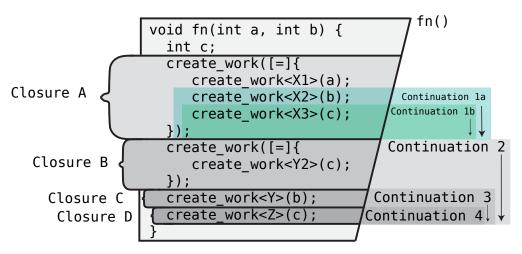

|    | 2.3   | DARN     | A Frontend Concepts and Components                          | 35 |

|    |       | 2.3.1    | Capture Hooks                                               | 37 |

|    |       | 2.3.2    | Dependency Capture                                          | 37 |

|    |       | 2.3.3    | Dependency Analysis                                         | 37 |

|    | 2.4   | DARN     | A Abstractions and Simple Examples                          | 37 |

|    | 2.5   | Backer   | nd Concepts and Components                                  | 38 |

|    |       | 2.5.1    | Future Work: Shifting Frontend and Backend Responsibilities | 41 |

| 3  | Find  | lings on | the Generality of the DARMA Backend API                     | 43 |

|    | 3.1   | CHAR     | M++                                                         | 44 |

|    |       | 3.1.1    | Introduction                                                | 44 |

|    |       | 3.1.2    | Challenges                                                  | 45 |

|    |       | 3.1.3    | Data and Task Collections                                   | 46 |

|   |      |          | 3.1.3.1      | Load Balancing                                 | 47 |

|---|------|----------|--------------|------------------------------------------------|----|

|   |      | 3.1.4    | Terminat     | ion Detection                                  | 48 |

|   |      | 3.1.5    | Collectiv    | /es                                            | 48 |

|   | 3.2  | OnNoo    | le           |                                                | 49 |

|   | 3.3  | HPX .    |              |                                                | 50 |

|   | 3.4  | MPI .    |              |                                                | 51 |

|   | 3.5  | Legior   | REALM        |                                                | 52 |

|   | 3.6  | Summ     | ary of Find  | dings                                          | 53 |

| 4 | Find | lings on | Interope     | rability                                       | 57 |

|   | 4.1  | Node-    | evel Reso    | urces                                          | 58 |

|   |      | 4.1.1    | Коккоз       | S: Performance Portability                     | 58 |

|   |      | 4.1.2    | AMT+K        | OKKOS: Design Challenges and Considerations    | 58 |

|   |      | 4.1.3    | DARMA        | A +KOKKOS: Strategy and Implementation Details | 59 |

|   | 4.2  | Netwo    | rk Resour    | ces                                            | 61 |

| 5 | Find | lings on | Performa     | ance and Productivity                          | 63 |

|   | 5.1  | Produc   | ctivity with | nin the DARMA Programming Model                | 63 |

|   | 5.2  | Trinity  | : Advance    | ed Technology System - 1                       | 65 |

|   |      | 5.2.1    | Haswell      | and KNL Differences                            | 66 |

|   | 5.3  | C++ C    | ompilers.    |                                                | 67 |

|   | 5.4  | Bench    | marks        |                                                | 68 |

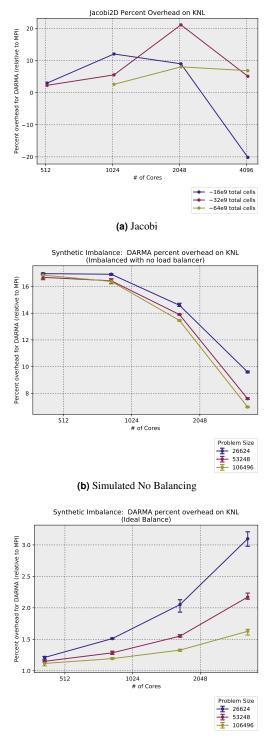

|   |      | 5.4.1    | Jacobi B     | enchmark                                       | 68 |

|   |      |          | 5.4.1.1      | CPU Binding and Affinity Study                 | 69 |

|   |      |          | 5.4.1.2      | Mutrino: 64 nodes                              | 69 |

|   |      |          | 5.4.1.3      | Detailed Performance Analysis for DARMA        | 70 |

|   |      |          | 5.4.1.4      | Trinity: 2048 nodes                            | 72 |

|   |      |          | 5.4.1.5      | Productivity and Semantic Information Gain     | 72 |

|   |      |          | 011110       | 5                                              |    |

|     |         | 5.4.2.1     | Mutrino: 64 nodes                          | 81  |

|-----|---------|-------------|--------------------------------------------|-----|

|     |         | 5.4.2.2     | Detailed Performance Analysis for DARMA    | 82  |

|     |         | 5.4.2.3     | Trinity: 2048 nodes                        | 82  |

|     |         | 5.4.2.4     | Productivity and Semantic Information Gain | 82  |

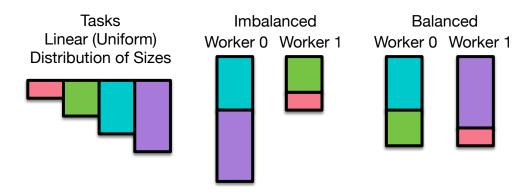

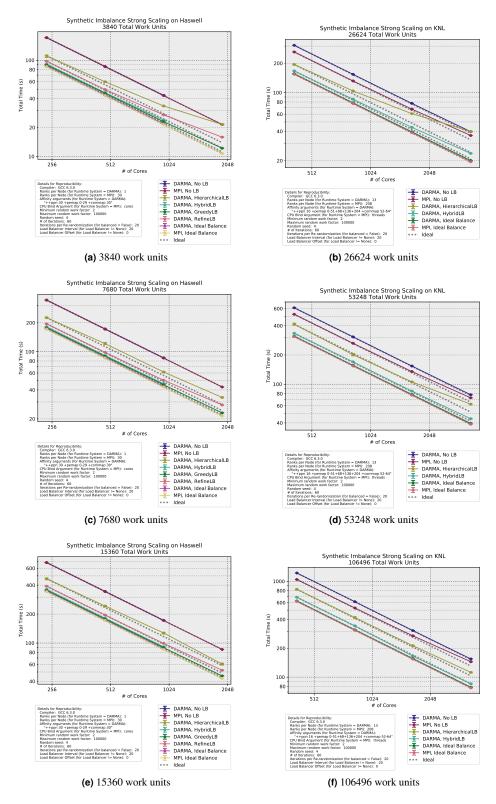

|     | 5.4.3   | Simulate    | d Load-Imbalance Benchmark                 | 90  |

|     |         | 5.4.3.1     | Mutrino: 64 nodes                          | 90  |

|     |         | 5.4.3.2     | Detailed Performance Analysis for DARMA    | 91  |

|     |         | 5.4.3.3     | Trinity: 2048 nodes                        | 92  |

|     |         | 5.4.3.4     | Productivity and Semantic Information Gain | 92  |

|     | 5.4.4   | Common      | n Trends Amongst Benchmarks                | 98  |

|     |         | 5.4.4.1     | Overhead relative to MPI on Haswell        | 98  |

|     |         | 5.4.4.2     | Overhead relative to MPI on KNL            | 98  |

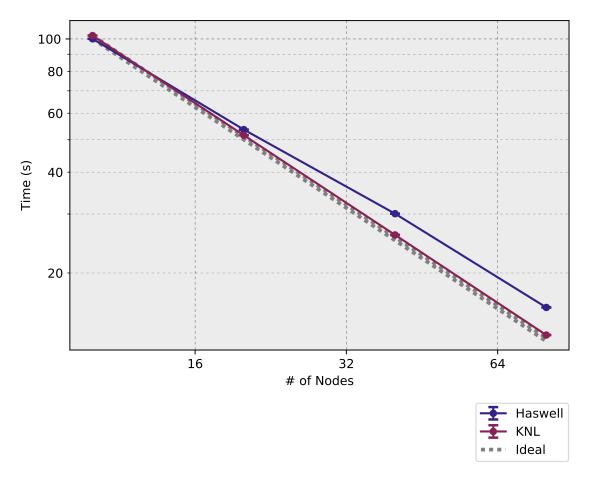

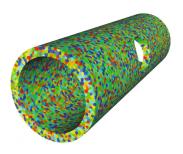

| 5.5 | Particl | e-in-Cell F | Proxy                                      | 101 |

|     | 5.5.1   | Backgrou    | und and Relevance to Sandia's ATDM Program | 101 |

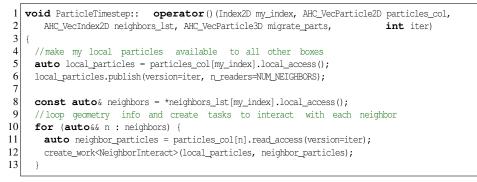

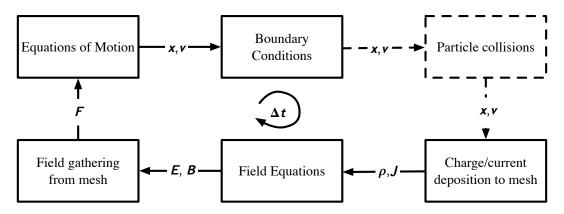

|     | 5.5.2   | Design o    | f SimplePIC                                | 102 |

|     | 5.5.3   | Performa    | ance of SIMPLEPIC on Target Architectures  | 104 |

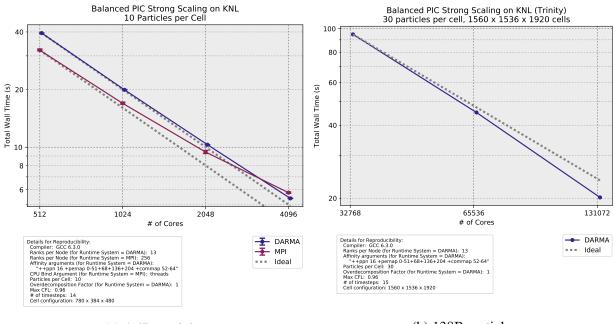

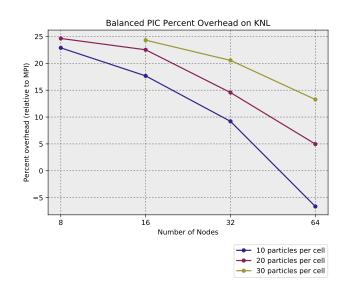

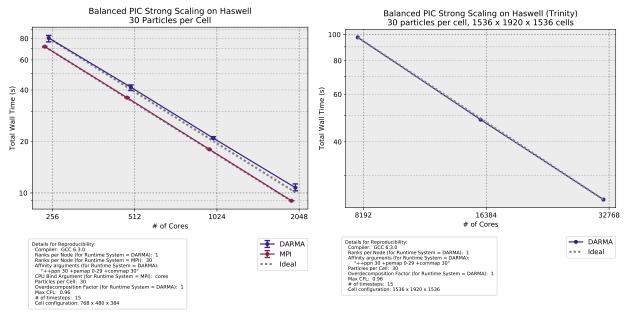

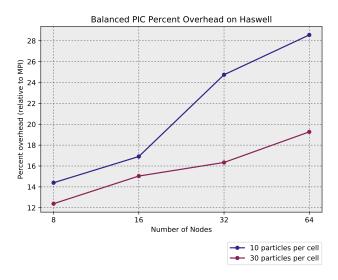

|     |         | 5.5.3.1     | Benchmark of Balanced PIC Problem          | 104 |

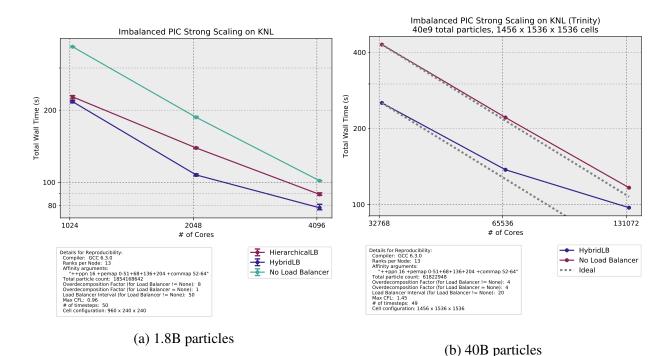

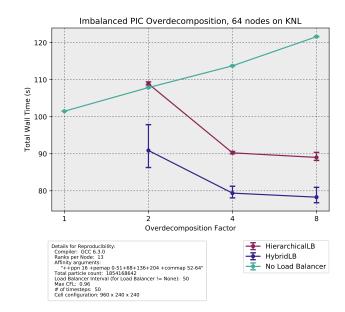

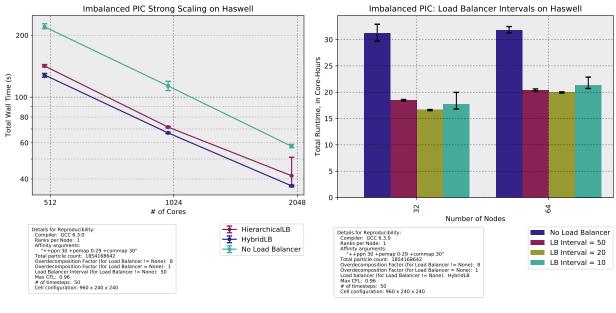

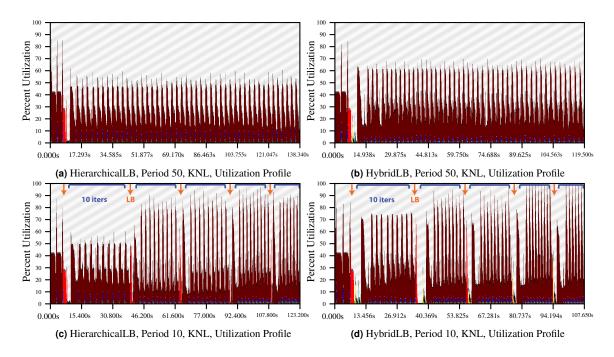

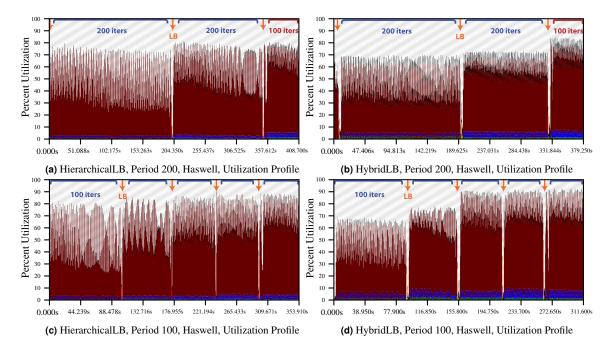

|     |         | 5.5.3.2     | Benchmark of Imbalanced PIC Problem        | 109 |

|     | 5.5.4   | Findings    | and Future Work                            | 113 |

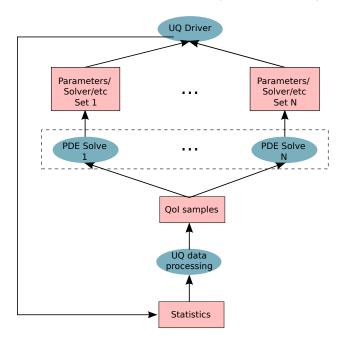

| 5.6 | Uncert  | ainty quan  | tification (UQ) Proxy                      | 115 |

|     | 5.6.1   | Backgrou    | und and Relevance to Sandia's ATDM Program | 115 |

|     | 5.6.2   | Design o    | f UQ Proxy                                 | 115 |

|     |         | 5.6.2.1     | Monte Carlo (MC) Methods                   | 116 |

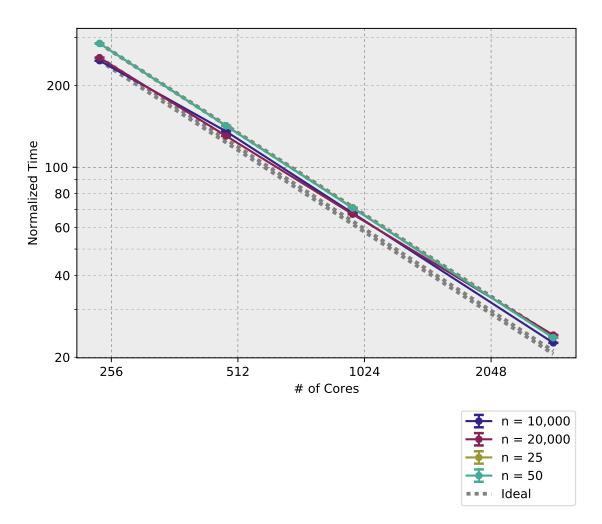

|     | 5.6.3   | Performa    | ance of UQ Proxy on Target Architectures   | 117 |

|     |         | 5.6.3.1     | Monte Carlo Example                        | 117 |

|     |         | 5.6.3.2     | Multi Level Monte Carlo Example            | 121 |

|     | 5.6.4   | Findings    | and Feedback                               | 122 |

| 5.7 | Multis  | cale Proxy  | ·                                          | 125 |

|   |     | 5.7.1    | Background and Relevance to Sandia's ATDM Program 1                 | 25  |

|---|-----|----------|---------------------------------------------------------------------|-----|

|   |     | 5.7.2    | Multiscale Proxy Design                                             | .25 |

|   |     |          | 5.7.2.1 Multiscale capability 1                                     | 26  |

|   |     |          | 5.7.2.2 Software Implementation Strategy 1                          | 28  |

|   |     | 5.7.3    | Preliminary Results 1                                               | .29 |

|   |     |          | 5.7.3.1 Single-Scale Simulation 1                                   | .29 |

|   |     |          | 5.7.3.2 Multiscale Simulation with Load Balancing 1                 | .30 |

|   |     | 5.7.4    | Findings and Feedback 1                                             | .32 |

| 6 | Con | clusions | and Recommendations 1                                               | 35  |

| 7 | Арр | endix    | 1                                                                   | 137 |

|   | 7.1 | Fronte   | nd Abstractions                                                     | .37 |

|   |     | 7.1.1    | Abstractions                                                        | .38 |

|   |     |          | 7.1.1.1 Distributable AAOs and Concurrent AECs                      | .39 |

|   |     |          | 7.1.1.2 Access Permissions 1                                        | .39 |

|   |     |          | 7.1.1.3 Tracking available access permissions of an AAO 1           | .42 |

|   |     | 7.1.2    | Execution of AECs 1                                                 | .45 |

|   | 7.2 | Backer   | nd Abstractions                                                     | .46 |

|   |     | 7.2.1    | The Use Life Cycle 1                                                | .46 |

|   |     | 7.2.2    | Flow s and AntiFlow s 1                                             | .47 |

|   |     | 7.2.3    | Handle s and SerializationManager 1                                 | .48 |

|   |     | 7.2.4    | Task s 1                                                            | .49 |

|   |     | 7.2.5    | UseCollection s and TaskCollection s 1                              | 50  |

|   |     | 7.2.6    | Task Migration                                                      | 51  |

|   |     | 7.2.7    | Publication and Collectives 1                                       | 51  |

|   | 7.3 | Future   | Work                                                                | 51  |

|   |     | 7.3.1    | Improvements for Interfacing with Mature Applications 1             | 51  |

|   |     |          | 7.3.1.1 Generalization of and Specialization Hooks for AccessHandle | .52 |

|            | 7.3.1.2 | Interfacing with Unmanaged Data | . 152 |

|------------|---------|---------------------------------|-------|

|            | 7.3.1.3 | DARMA Regions                   | . 152 |

| Glossary   |         |                                 | 154   |

| References |         |                                 | 160   |

# **List of Figures**

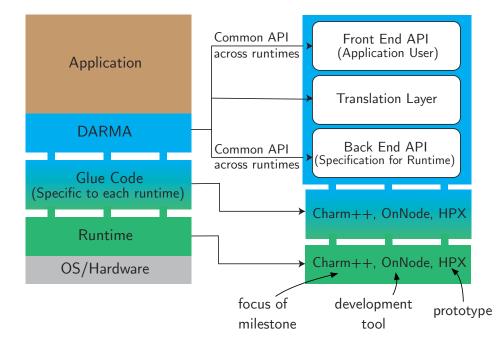

| 2.1 | The components of DARMA within the context of a generic DARMA-compliant software stack.                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

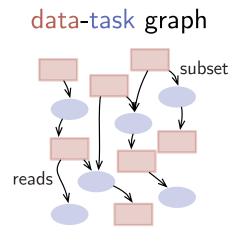

| 2.2 | AMT runtimes operate with a directed acyclic graph (DAG) that captures relationships be-<br>tween application data and inter-dependent tasks. DAGs can be annotated to capture addi-<br>tional information such as a tasks' read/write usage of data, or whether a task needs a subset<br>of a particular piece of data only. This additional information enables a runtime to reason<br>more completely about when and where to execute a task and whether to load balance | 34 |

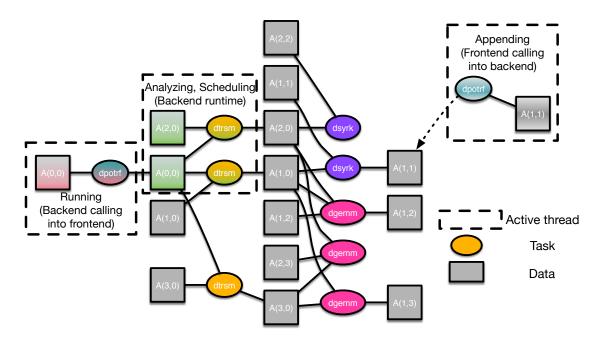

| 2.3 | The DARMA execution model showing simultaneous consuming and producing of a task-<br>DAG for Cholesky decomposition. Three parallel threads are shown that are 1) running an<br>active task, 2) scheduling pending tasks, and 3) appending new tasks to execute. Note this<br>is a conceptual model only and not a strict requirement                                                                                                                                       | 36 |

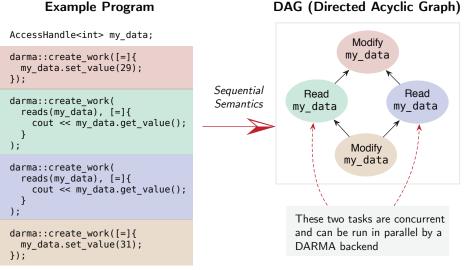

| 2.4 | Simple examples putting data and tasks together.                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

|     | (a) AccessHandle and create_work                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

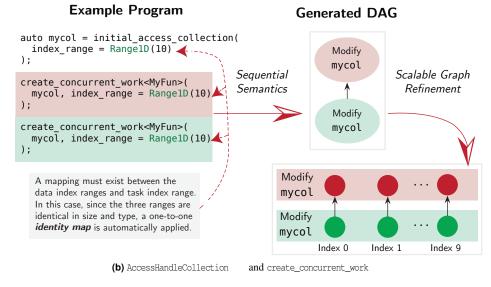

|     | (b) AccessHandleCollection and create_concurrent_work                                                                                                                                                                                                                                                                                                                                                                                                                       | 39 |

| 2.5 | Example DARMA code that performs a SAXPY on the distributed collections: A, x, y                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

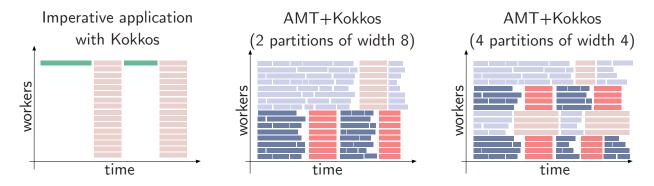

| 4.1 | A comparison of worker activity over time for several application scenarios. On the left, a simple imperative application code is shown with serial work in green and KOKKOS work in red. The middle and right images illustrate AMT+KOKKOS for two different partitionings of resources. The threaded AMT work is shown in blue and the KOKKOS work is shown in red.                                                                                                       | 58 |

| 4.2 | Example code comprising both KOKKOS and DARMA.                                                                                                                                                                                                                                                                                                                                                                                                                              | 60 |

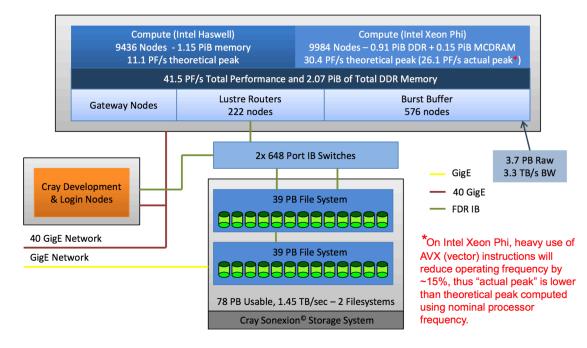

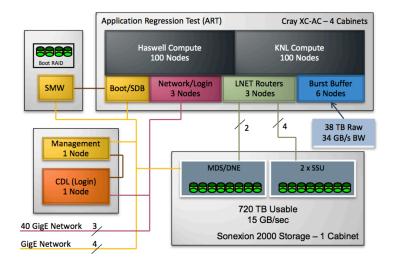

| 5.1 | An overview of the Trinity Architecture (image courtesy of ACES)                                                                                                                                                                                                                                                                                                                                                                                                            | 66 |

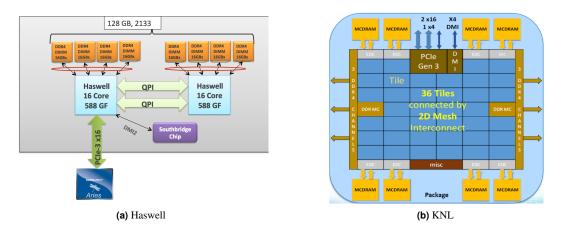

| 5.2 | Diagrams of Haswell and KNL compute nodes on the left and right respectively (images courtesy of ACES).                                                                                                                                                                                                                                                                                                                                                                     | 66 |

|     | (a) Haswell                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66 |

|     | (b) KNL                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66 |

| 5.3 | An overview of the Mutrino Architecture (image courtesy of ACES)                                                                                                                                                                                                                                                                                                                                                                                                            | 67 |

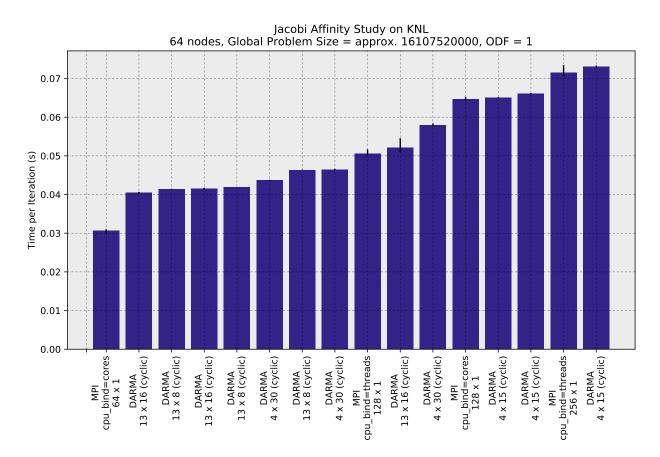

| 5.4 | MPI<br>value                                      | rved performance for varying CPU binding/affinity configurations on Haswell for both<br>and DARMA on Jacobi benchmark for 64 nodes of KNL. Error bars show min and max<br>as observed from multiple trials. Binding configurations examine number of processes<br>ode, number of threads per process, and use of hyperthreading                                                                                                                                                                                                                                                                      | 70 |

|-----|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

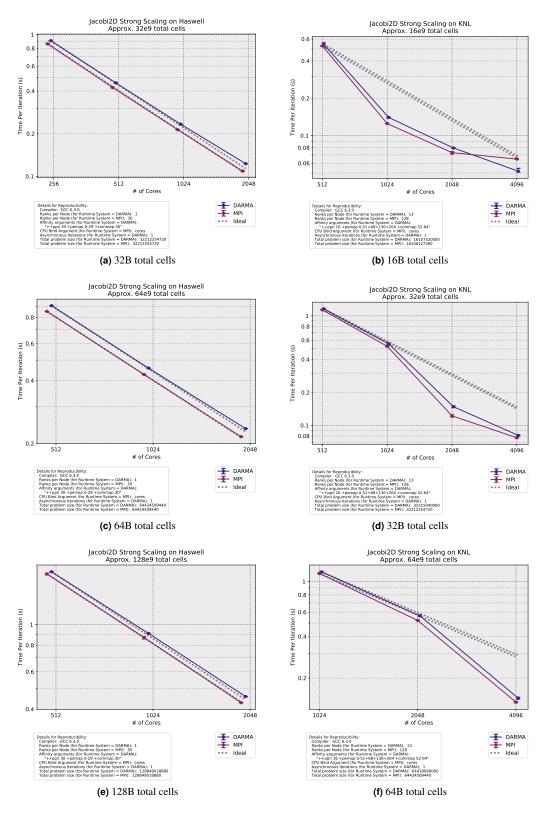

| 5.5 | creas<br>KNL<br>show                              | g scaling performance of Jacobi benchmark for MPI and DARMA-CHARM++ for in-<br>ing total cells on Mutrino for Haswell (2048 cores): (a) 32B, (c) 64B, and (e) 128B and<br>(4096 cores): (b) 16B, (d) 32B, and (f) 64B. Note scales do not begin at 0. Error bars<br>min and max values observed from multiple trials. All-Reduce convergence checks                                                                                                                                                                                                                                                  | 74 |

|     | are p                                             | erformed each iteration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74 |

|     | (a)                                               | 32B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74 |

|     | (b)                                               | 16B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74 |

|     | (c)                                               | 64B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74 |

|     | (d)                                               | 32B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74 |

|     | (e)                                               | 128B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

|     | (f)                                               | 64B total cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74 |

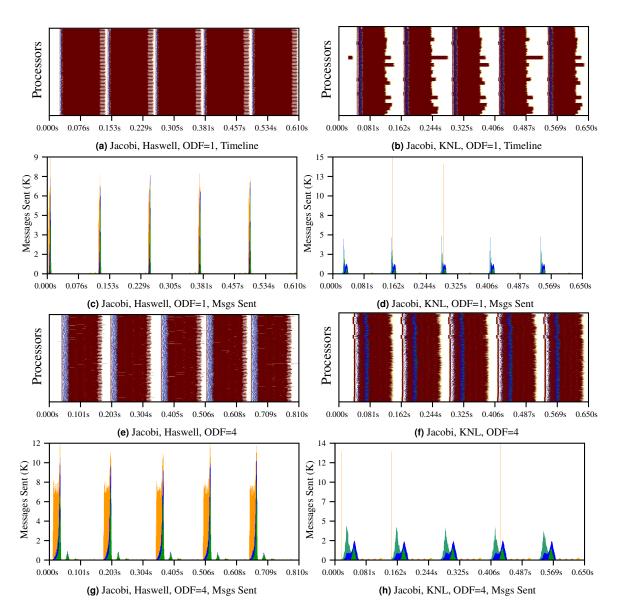

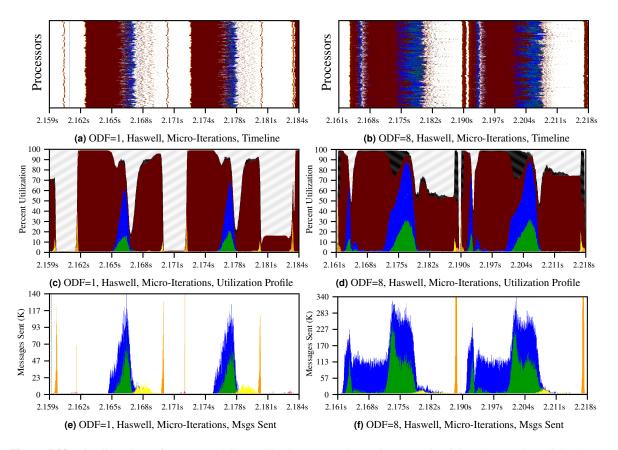

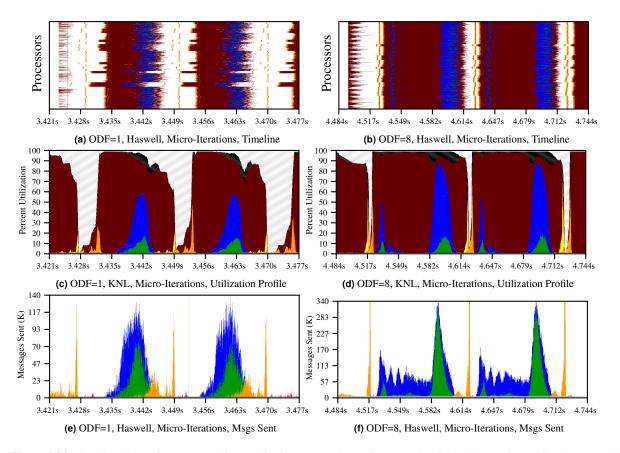

| 5.6 | Jacob<br>level<br>while<br>clear<br>duce<br>ing b | line views and communication histograms for a sample of threads over time of the bi benchmark (in DARMA) on 64 nodes of Mutrino (Haswell and KNL) for varying s of overdecomposition. In the timeline views, task execution is indicated in maroon e idle time is shown in white. Computation stalls at regular intervals. The timeline ly shows a gap where task execution stalls which corresponds to the residual allre By increasing overdecomposition, messages sent are more spread out over time, causetter network utilization, effective communication/computation overlap, but the cost of |    |

|     | depe                                              | ndency analysis (in orange) slightly increases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

|     | (a)                                               | Jacobi, Haswell, ODF=1, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75 |

|     | (b)                                               | Jacobi, KNL, ODF=1, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75 |

|     | (c)                                               | Jacobi, Haswell, ODF=1, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75 |

|     | (d)                                               | Jacobi, KNL, ODF=1, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75 |

|     | (e)                                               | Jacobi, Haswell, ODF=4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75 |

|     | (f)                                               | Jacobi, KNL, ODF=4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |

|     | (g)                                               | Jacobi, Haswell, ODF=4, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75 |

|     | (h)                                               | Jacobi, KNL, ODF=4, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75 |

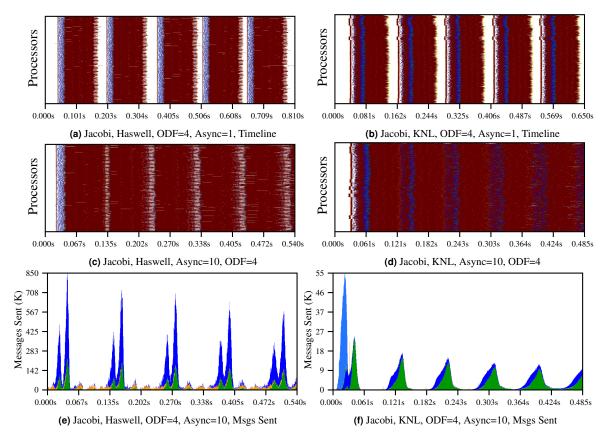

| 5.7 Timeline views and communication histograms for a sample of threads over time of the Jacobi benchmark (in DARMA) on 64 nodes of Mutrino (Haswell and KNL) for varying levels of asynchrony in the benchmark, achieved by incorporating speculative execution (async=1 or async=10). Computation is shown in maroon while idle time is in white. The overdecomposition factor (ODF) is fixed at 4. Asynchrony has a dramatic effect on the amount of idle time in the Jacobi benchmark. By reducing the hard, global synchroniz tion each iteration the idle time is reduced and the performance increases (compared to the previous best performance: async=10 is 13% faster on Haswell and 34% faster on KNL). |                          |                                                                                                                                                                                                                                                                      |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>(async=1 or async=10). Computation is shown in maroon while idle time is in white. To overdecomposition factor (ODF) is fixed at 4. Asynchrony has a dramatic effect on a amount of idle time in the Jacobi benchmark. By reducing the hard, global synchronization each iteration the idle time is reduced and the performance increases (compared to previous best performance: async=10 is 13% faster on Haswell and 34% faster on KNL)</li> <li>(a) Jacobi, Haswell, ODF=4, Async=1, Timeline</li></ul>                                                                                                                                                                                                | 76                       |                                                                                                                                                                                                                                                                      |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (a)                      | Jacobi, Haswell, ODF=4, Async=1, Timeline                                                                                                                                                                                                                            | 76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (b)                      | Jacobi, KNL, ODF=4, Async=1, Timeline                                                                                                                                                                                                                                | 76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (c)                      | Jacobi, Haswell, Async=10, ODF=4                                                                                                                                                                                                                                     | 76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (d)                      | Jacobi, KNL, Async=10, ODF=4                                                                                                                                                                                                                                         | 76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (e)                      | Jacobi, Haswell, ODF=4, Async=10, Msgs Sent                                                                                                                                                                                                                          | 76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (f)                      | Jacobi, KNL, ODF=4, Async=10, Msgs Sent                                                                                                                                                                                                                              | 76 |

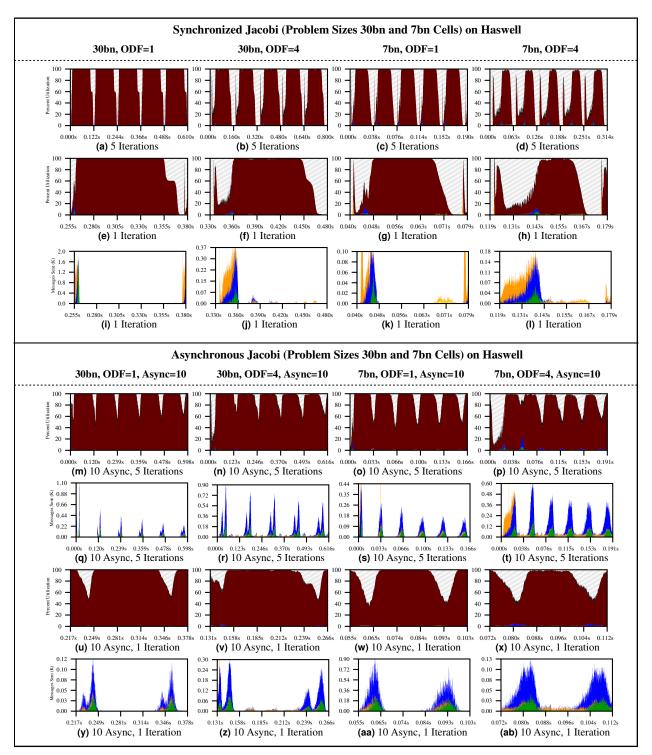

| 5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | the Ja<br>explo<br>total | acobi benchmark (in DARMA) on 64 nodes of Mutrino on Haswell. Different columns<br>ore varying levels of overdecomposition for two problems sizes (7bn total cells and 30bn<br>cells). Different rows explore varying levels of asynchrony exposed in the benchmark. | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (a)                      | 5 Iterations                                                                                                                                                                                                                                                         | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (b)                      | 5 Iterations                                                                                                                                                                                                                                                         | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (c)                      | 5 Iterations                                                                                                                                                                                                                                                         | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (d)                      | 5 Iterations                                                                                                                                                                                                                                                         | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (e)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (f)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (g)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (h)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (i)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (j)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (k)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (1)                      | 1 Iteration                                                                                                                                                                                                                                                          | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                                                                                                                                                                                                                                                                      |    |

|      | (n)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (0)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (p)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (q)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (r)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (s)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (t)            | 10 Async, 5 Iterations                                                                                                                                                                                                                                                                             | 77 |

|      | (u)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (v)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (w)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (x)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (y)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (z)            | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (aa)           | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

|      | (ab)           | 10 Async, 1 Iteration                                                                                                                                                                                                                                                                              | 77 |

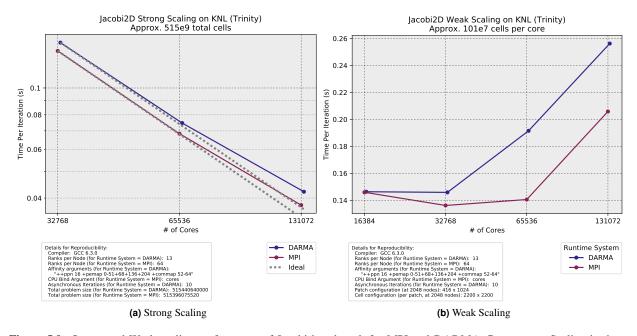

| 5.9  | Scalin and m   | g and Weak scaling performance of Jacobi benchmark for MPI and DARMA-CHARM++.<br>ng is shown up to 2048 nodes on Trinity for KNL (139K cores). Error bars show min<br>nax values observed from multiple trials. The overdecomposition factor is set to 4 for<br>MA                                 |    |

|      | (a)            | Strong Scaling                                                                                                                                                                                                                                                                                     | 78 |

|      | (b)            | Weak Scaling                                                                                                                                                                                                                                                                                       | 78 |

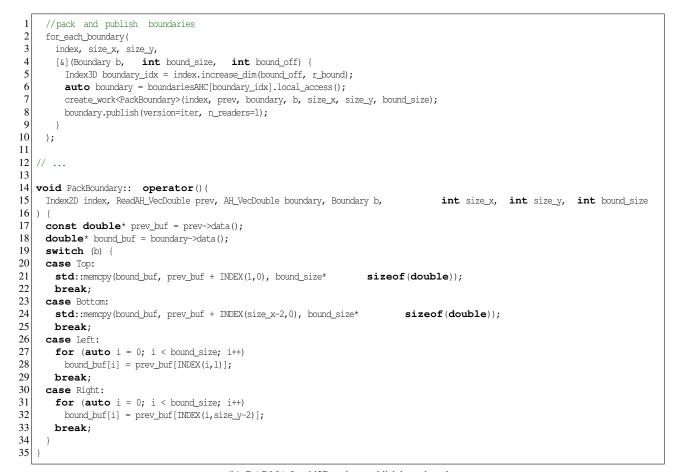

| 5.10 |                | and DARMA Jacobi2D code to pack and send boundaries in overdecomposed imple-                                                                                                                                                                                                                       | 79 |

|      | (a)            | MPI Jacobi2D code to send boundaries in overdecomposed implementation                                                                                                                                                                                                                              | 79 |

|      | (b)            | DARMA Jacobi2D code to publish boundary data.                                                                                                                                                                                                                                                      | 79 |

| 5.11 | pleme<br>opera | barison of the DARMA and MPI Jacobi2D code for the timestepping loop. Both im-<br>entations include overdecomposition and a global convergence check via a reduce<br>tion, The DARMA implementation includes asynchronous iterations (lines 14–20),<br>e MPI code is synchronized every iteration. | 80 |

|      | (a)            | MPI Jacobi2D outer timestepping loop with overdecomposition.                                                                                                                                                                                                                                       | 80 |

|      | (b)                                             | DARMA Jacobi2D outer timestepping loop with overdecomposition and substeps (asynchronous iterations).                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80 |

|------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

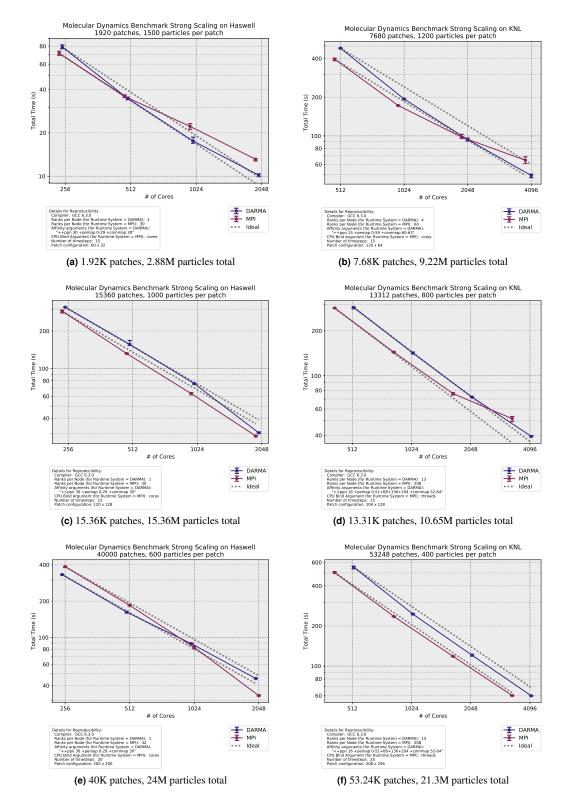

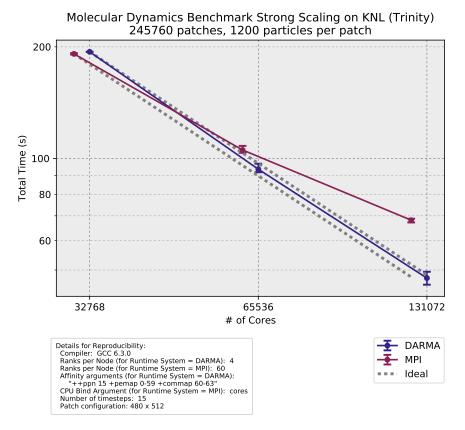

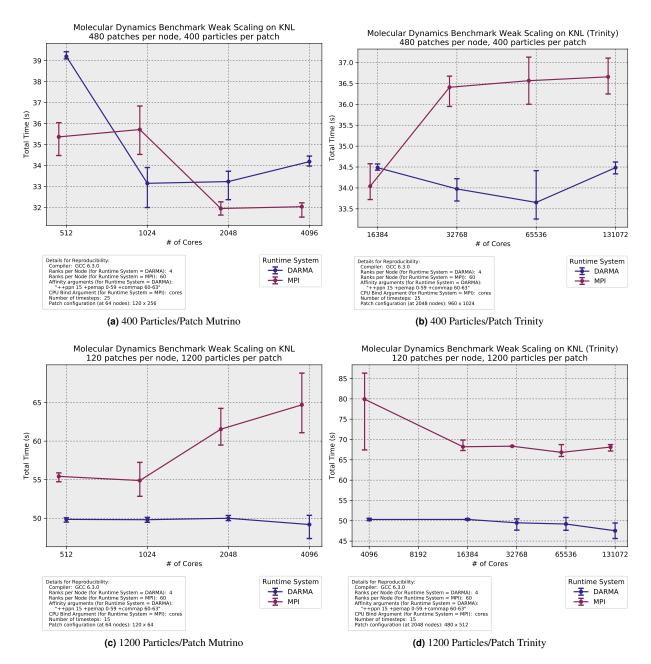

| 5.12 | CHAI<br>for M<br>colum                          | g scaling performance of molecular dynamics benchmark for MPI and DARMA-<br>RM++ for varying problem sizes. Scaling is shown up to 64 nodes in the left column<br>Iutrino for Haswell (1920 cores for MPI, 1984 cores for DARMA) and in the right<br>on for KNL (3840 cores for MPI, 4096 cores for DARMA). Error bars show min and<br>values observed from multiple trials.                                                                                                                                                                                     | 84 |

|      | (a)                                             | 1.92K patches, 2.88M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84 |

|      | (b)                                             | 7.68K patches, 9.22M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84 |

|      | (c)                                             | 15.36K patches, 15.36M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84 |

|      | (d)                                             | 13.31K patches, 10.65M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84 |

|      | (e)                                             | 40K patches, 24M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84 |

|      | (f)                                             | 53.24K patches, 21.3M particles total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84 |

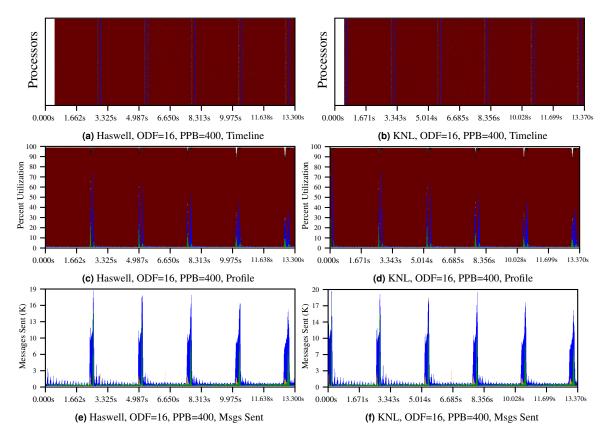

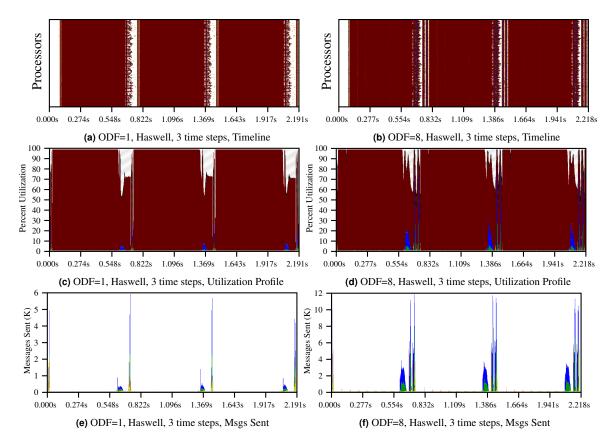

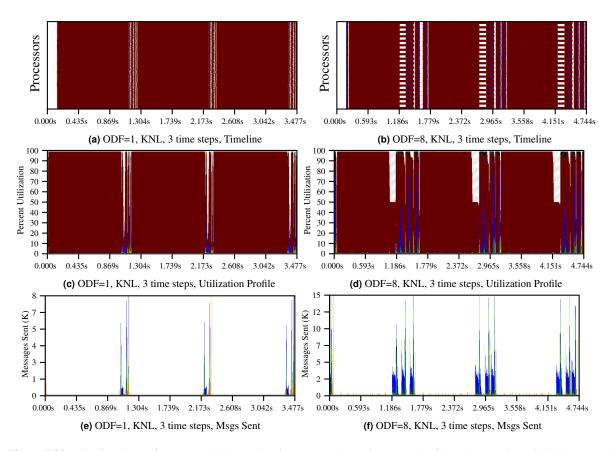

| 5.13 | box o<br>tivity<br>indica<br>over t<br>munic    | lines showing activity of the molecular dynamics benchmark with 400 particles per<br>on Haswell and KNL partitions of Mutrino. (a) and (b) show compute/system/idle ac-<br>over time on a per-processor basis. Maroon indicates task computation while blue<br>ates idle time or system work. (c) and (d) show percent utilization of the processors<br>time, with periods of intense computation (all maroon) interspersed with idle and com-<br>cation activity. (e) and (f) show messages sent in certain time windows, demonstrating<br>munication activity. | 85 |

|      | (a)                                             | Haswell, ODF=16, PPB=400, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85 |

|      | (b)                                             | KNL, ODF=16, PPB=400, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85 |

|      | (c)                                             | Haswell, ODF=16, PPB=400, Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85 |

|      | (d)                                             | KNL, ODF=16, PPB=400, Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85 |

|      | (e)                                             | Haswell, ODF=16, PPB=400, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85 |

|      | (f)                                             | KNL, ODF=16, PPB=400, Msgs Sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85 |

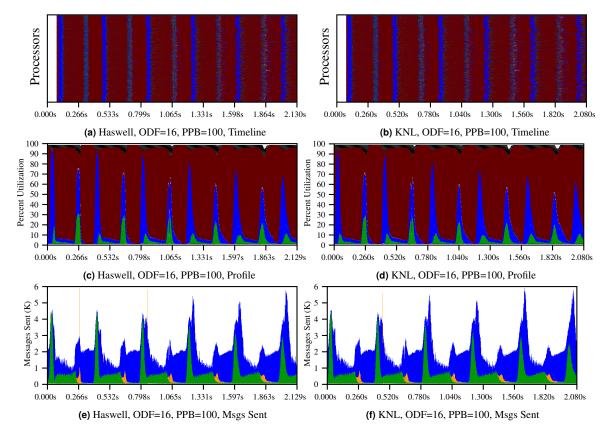

| 5.14 | on Ha<br>over t<br>time of<br>period<br>ity. (e | lines showing activity of the molecular dynamics benchmark with 100 particles per box<br>aswell and KNL partitions of Mutrino. (a) and (b) show compute/system/idle activity<br>time on a per-processor basis. Red indicates task computation while blue indicates idle<br>or system work. (c) and (d) show percent utilization of the processors over time, with<br>ds of intense computation (all maroon) interspersed with idle and communication activ-<br>e) and (f) show messages sent in certain time windows, demonstrating communication<br>ty.         | 86 |

|      | (a)                                             | Haswell, ODF=16, PPB=100, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86 |

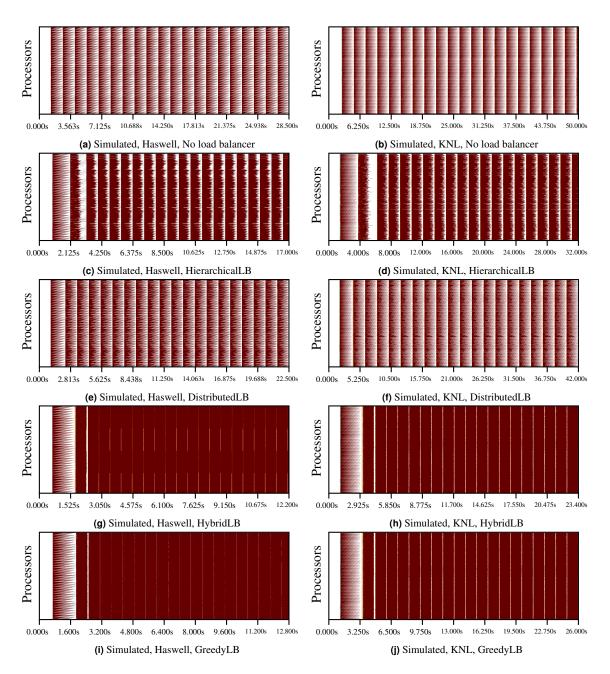

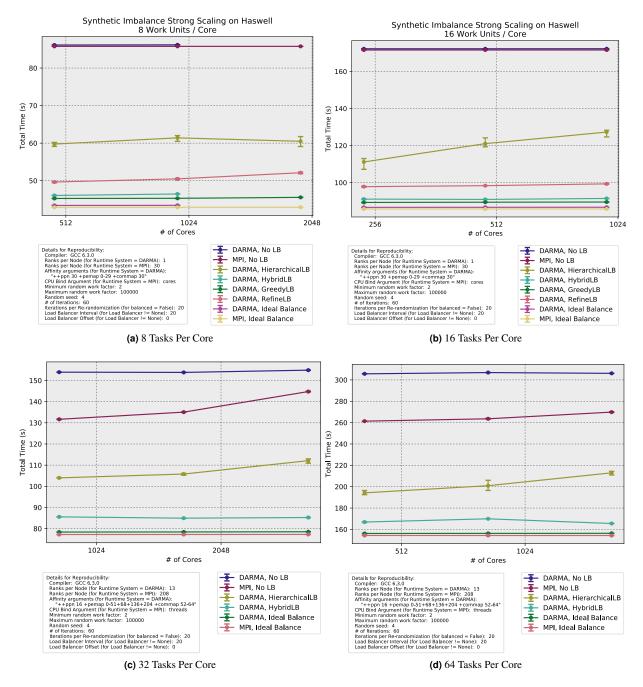

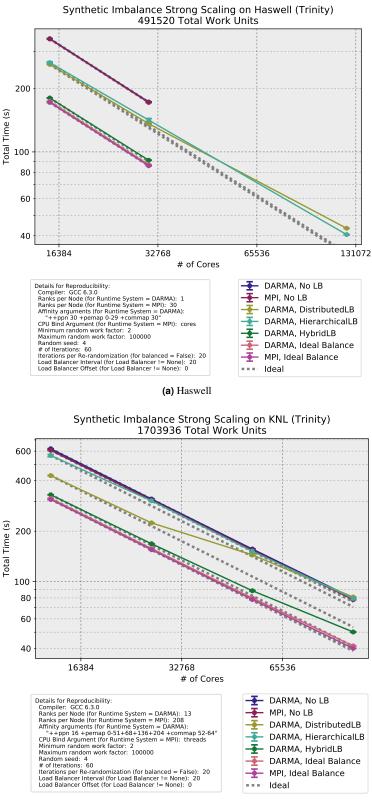

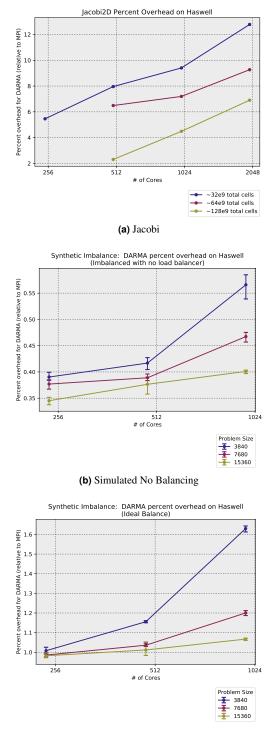

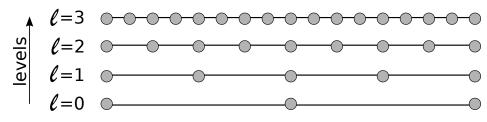

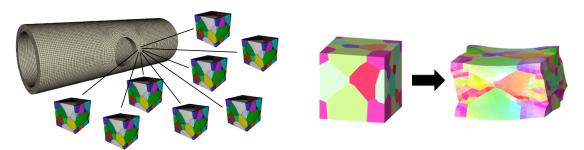

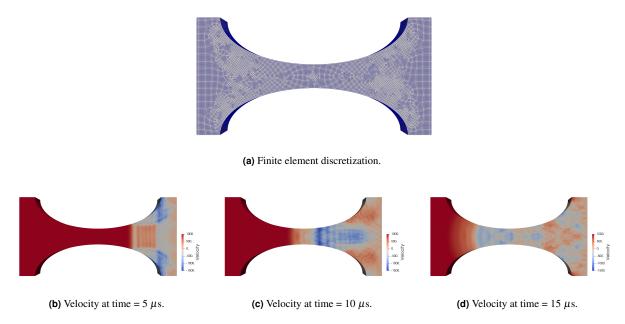

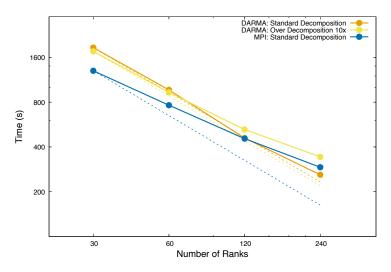

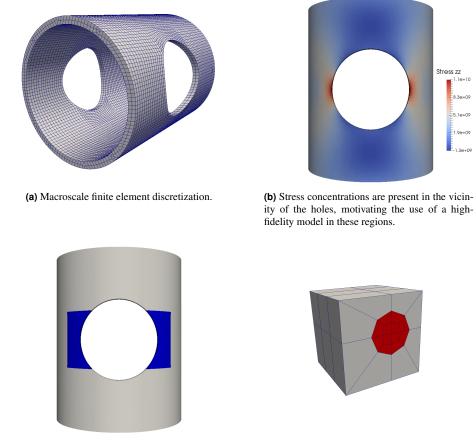

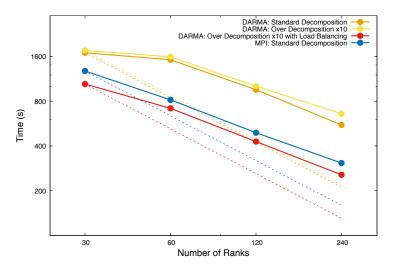

|      | (b)                                             | KNL, ODF=16, PPB=100, Timeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86 |